a) Prosedur

b) Hardware

c) Rangkaian Simulasi dan Prinsip Kerja

d) Flowchart

e) Video Demo

f) Download File

1. Pendahuluan [Kembali]

2. Tujuan [Kembali]

- Merancang sistem kontrol akuarium berbasis sistem digital yang bekerja secara otomatis.

- Mengimplementasikan sensor water level untuk mendeteksi ketinggian air akuarium dan mengendalikan pompa air secara otomatis.

- Mengimplementasikan touch sensor sebagai pemicu sistem pemberi pakan ikan.

- Menerapkan konsep-konsep sistem digital dalam pengolahan sinyal input dan pengendalian output.

2. Alat dan Bahan [Kembali]

Alat :

1. Voltmeter

Ampermeter adalah alat ukur listrik yang digunakan untuk mengukur besar arus listrik (I) yang mengalir pada suatu rangkaian. Satuan yang digunakan adalah Ampere (A), sesuai dengan hukum Ohm dan konsep dasar arus listrik. Agar pembacaan akurat, ampermeter harus disusun secara seri dengan beban sehingga seluruh arus yang mengalir ke beban juga melewati ampermeter.

Spesifikasi:

Bahan :

1. Touch Sensor

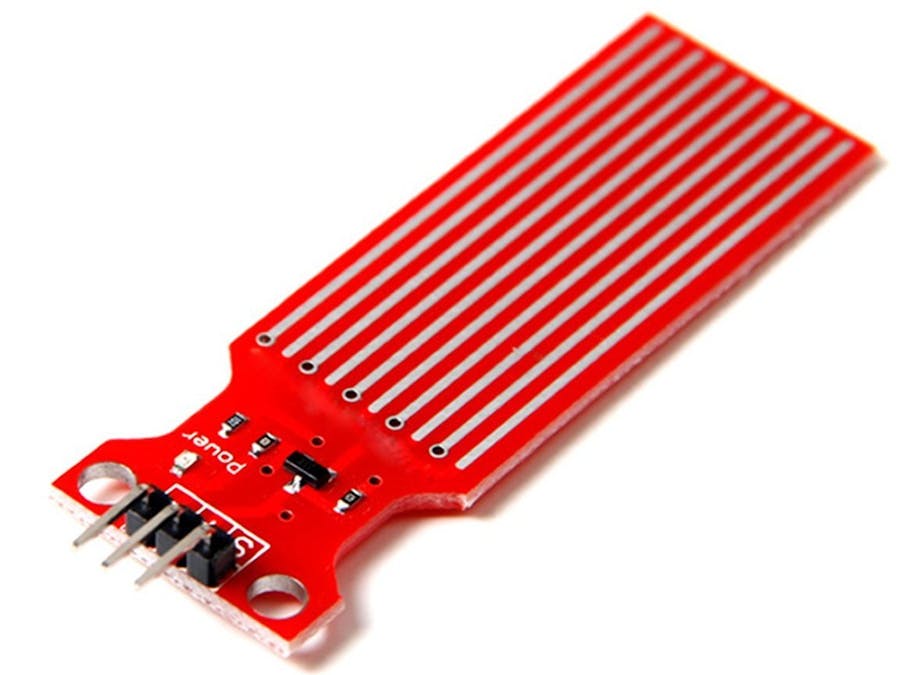

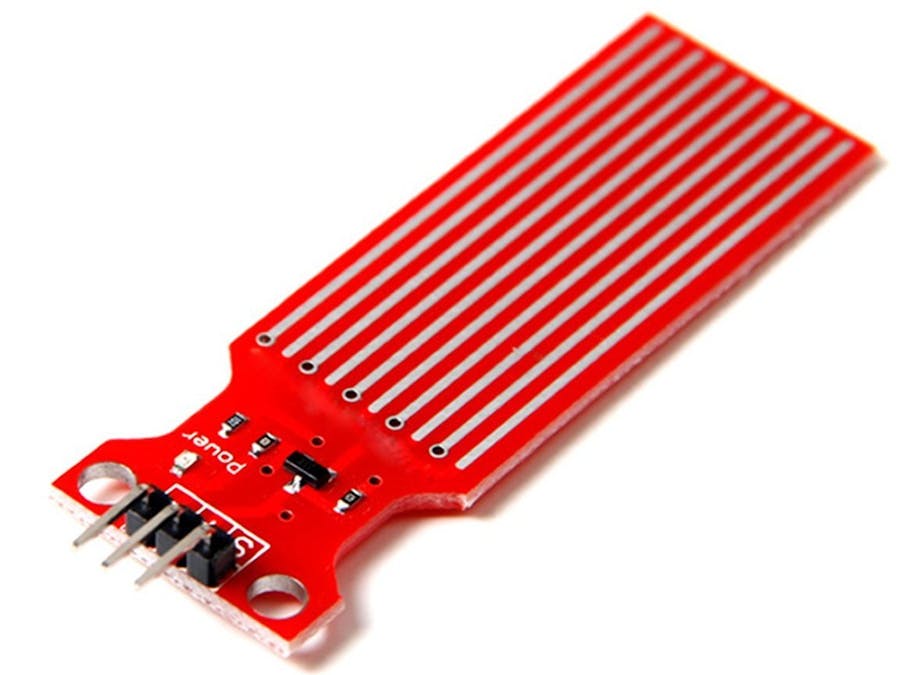

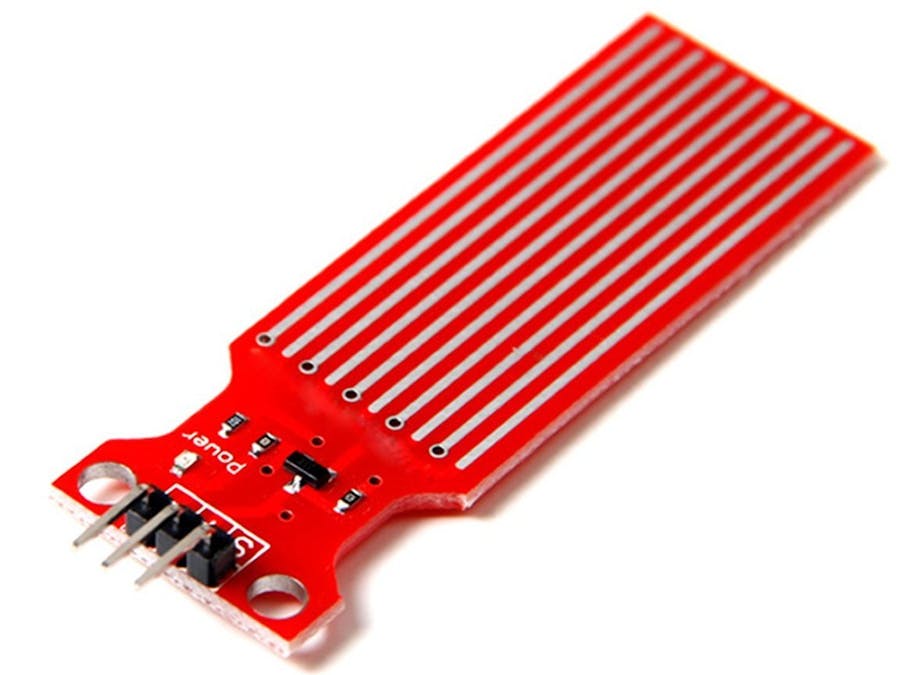

2. Water level sensor

3. Resistor

Resistor adalah komponen Elektronika Pasif yang memiliki nilai resistansi atau hambatan tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu rangkaian Elektronika (V=I R). Jenis Resistor yang digunakan disini adalah Fixed Resistor, dimana merupakan resistor dengan nilai tetap terdiri dari film tipis karbon yang diendapkan subtrat isolator kemudian dipotong berbentuk spiral. Keuntungan jenis fixed resistor ini dapat menghasilkan resistor dengan toleransi yang lebih rendah.Cara menghitung nilai resistor:Tabel warnaSpesifikasi.jpeg)

2. Water level sensor

.jpeg)

5. Kabel Jumper

9. LM 158

LM158 adalah jenis operational amplifier (op-amp) yang terdiri dari dua penguat operasional dalam satu kemasan dan dirancang untuk aplikasi penguatan sinyal analog.

Spesifikasi:

Sebagai keluaran (output) yang menyatakan rangkaian jalan ketika motor hidup.

3. Dasar Teori [Kembali]

1. TOUCH SENSOR

Touch sensor adalah sebuah sensor yang berfungsi untuk mendeteksi adanya sentuhan dari jari manusia atau benda konduktif lainnya. Sensor ini bekerja berdasarkan perubahan sifat listrik, terutama kapasitansi, ketika permukaan sensor disentuh. Tubuh manusia memiliki muatan listrik alami sehingga saat terjadi sentuhan, nilai kapasitansi pada sensor berubah dan diolah oleh rangkaian internal menjadi sinyal keluaran berupa logika digital HIGH atau LOW. Oleh karena itu, touch sensor dapat digunakan sebagai pengganti tombol mekanik konvensional.

Dalam penggunaannya, touch sensor memiliki kelebihan karena tidak memerlukan tekanan fisik, memiliki respon yang cepat, dan umur pakai yang lebih panjang dibandingkan push button biasa. Sensor ini juga mudah diintegrasikan dengan rangkaian digital seperti gerbang logika, flip-flop, dan counter, sehingga sangat cocok digunakan pada sistem kontrol otomatis. Namun, touch sensor memiliki kelemahan yaitu sensitif terhadap gangguan lingkungan seperti kelembapan dan noise listrik, sehingga perlu perancangan rangkaian yang baik. Touch sensor banyak diaplikasikan pada panel kontrol modern, sistem keamanan, peralatan elektronik rumah tangga, serta sistem kontrol aquarium otomatis sebagai input untuk mengaktifkan atau menonaktifkan aktuator seperti motor, pompa, aerator, atau buzzer.

2. Water Level Sensor

Water level sensor adalah sensor yang digunakan untuk mendeteksi ketinggian atau level air di dalam suatu wadah atau tangki. Sensor ini bekerja dengan memanfaatkan sifat konduktivitas air atau perubahan resistansi ketika air menyentuh titik sensor tertentu. Saat permukaan air mencapai level yang telah ditentukan, sensor akan menghasilkan sinyal keluaran berupa perubahan tegangan atau logika digital yang menandakan kondisi air rendah, normal, atau tinggi. Informasi ini kemudian dapat digunakan sebagai input bagi sistem kontrol.

Dalam sistem kontrol otomatis, water level sensor berfungsi untuk mencegah kondisi air terlalu rendah atau meluap. Sensor ini banyak digunakan karena rangkaiannya sederhana, mudah diintegrasikan dengan sistem digital, dan cukup andal untuk pemantauan level air. Output dari water level sensor dapat dihubungkan ke rangkaian logika, komparator, atau flip-flop untuk mengendalikan aktuator seperti pompa air, relay, LED indikator, atau alarm. Meskipun demikian, water level sensor memiliki keterbatasan seperti sensitivitas terhadap kotoran dan kerak air, sehingga diperlukan perawatan berkala agar kinerjanya tetap optimal.

3. Motor DC

4. Resistor

Ie = Ic + Ib

Keterangan :

Ie = Arus Emitter

Ic = Arus Collector

Ib = Arus Basis

Keterangan :

Ie = Arus Emitter

Ic = Arus Collector

Op-Amp adalah salah satu dari bentuk IC Linear yang berfungsi sebagai Penguat Sinyal listrik. Sebuah Op-Amp terdiri dari beberapa Transistor, Dioda, Resistor dan Kapasitor yang terinterkoneksi dan terintegrasi sehingga memungkinkannya untuk menghasilkan Gain (penguatan) yang tinggi pada rentang frekuensi yang luas.

Simbol

Karakteristik IC OpAmp

- Penguatan Tegangan Open-loop atau Av = ∞ (tak terhingga)

- Tegangan Offset Keluaran (Output Offset Voltage) atau Voo = 0 (nol)

- Impedansi Masukan (Input Impedance) atau Zin= ∞ (tak terhingga)

- Impedansi Output (Output Impedance ) atau Zout = 0 (nol)

- Lebar Pita (Bandwidth) atau BW = ∞ (tak terhingga)

- Karakteristik tidak berubah dengan suhu

Secara umum, gerbang logika OR adalah komponen dasar dalam elektronika dan sistem digital yang beroperasi dengan dasar prinsip aljabar Boolean. Lebih lanjut, gerbang ini mengambil dua atau lebih input dan menghasilkan satu output. Fungsi utama dari gerbang OR adalah memberikan output bernilai tinggi jika setidaknya satu dari bernilai tinggi. Dengan kata lain, jika salah satu atau lebih dari input-nya ‘true’ atau ‘1’, maka output-nya akan ‘true’ atau ;1’.

Hanya ketika semua input-nya ‘false’ atau ‘0’, output-nya akan ‘true atau ‘1’. Secara keseluruhan, gerbang OR sangat penting dalam pembangunan sirkuit digital. Pasalnya, gerbang ini memungkinkan pelaksanaan fungsi logika dasar yang digunakan dalam berbagai aplikasi komputasi. Hal tersebut meliputi pemrosesan data sederhana hingga operasi yang lebih kompleks dalam sistem komputer dan elektronik.

8. Sevent Segment Seven segment merupakan bagian-bagian yang digunakan untuk menampilkan angka atau bilangan decimal. Seven segment tersebut terbagi menjadi 7 batang LED yang disusun membentuk angka 8 dengan menggunakan huruf a-f yang disebut DOT MATRIKS. Setiap segment ini terdiri dari 1 atau 2 LED (Light Emitting Dioda). Seven segment bisa menunjukan angka-angka desimal serta beberapa bentuk tertentu melalui gabungan aktif atau tidaknya LED penyususnan dalam seven segment.

Supaya memudahkan penggunaannnya biasanya memakai sebuah sebuah seven segment driver yang akan mengatur aktif atau tidaknya led-led dalam seven segment sesuai dengan inputan biner yang diberikan. Bentuk tampilan modern disusun sebagai metode 7 bagian atau dot matriks. Jenis tersebut sama dengan namanya, menggunakan sistem tujuh batang led yang dilapis membentuk angka 8 seperti yang ditunjukkan pada gambar di atas. Huruf yang dilihatkan dalam gambar itu ditetapkan untuk menandai bagian-bagian tersebut.

Dengan menyalakan beberapa segmen yang sesuai, akan dapat diperagakan digit-digit dari 0 sampai 9, dan juga bentuk huruf A sampai F (dimodifikasi). Sinyal input dari switches tidak dapat langsung dikirimkan ke peraga 7 bagian, sehingga harus menggunakan decoder BCD (Binary Code Decimal) ke 7 segmen sebagai antar muka. Decoder tersebut terbentuk dari pintu-pintu akal yang masukannya berbetuk digit BCD dan keluarannya berupa saluran-saluran untuk mengemudikan tampilan 7 segmen.

Tabel Pengaktifan Seven Segment Display

Seven segment merupakan bagian-bagian yang digunakan untuk menampilkan angka atau bilangan decimal. Seven segment tersebut terbagi menjadi 7 batang LED yang disusun membentuk angka 8 dengan menggunakan huruf a-f yang disebut DOT MATRIKS. Setiap segment ini terdiri dari 1 atau 2 LED (Light Emitting Dioda). Seven segment bisa menunjukan angka-angka desimal serta beberapa bentuk tertentu melalui gabungan aktif atau tidaknya LED penyususnan dalam seven segment.

Supaya memudahkan penggunaannnya biasanya memakai sebuah sebuah seven segment driver yang akan mengatur aktif atau tidaknya led-led dalam seven segment sesuai dengan inputan biner yang diberikan. Bentuk tampilan modern disusun sebagai metode 7 bagian atau dot matriks. Jenis tersebut sama dengan namanya, menggunakan sistem tujuh batang led yang dilapis membentuk angka 8 seperti yang ditunjukkan pada gambar di atas. Huruf yang dilihatkan dalam gambar itu ditetapkan untuk menandai bagian-bagian tersebut.

Dengan menyalakan beberapa segmen yang sesuai, akan dapat diperagakan digit-digit dari 0 sampai 9, dan juga bentuk huruf A sampai F (dimodifikasi). Sinyal input dari switches tidak dapat langsung dikirimkan ke peraga 7 bagian, sehingga harus menggunakan decoder BCD (Binary Code Decimal) ke 7 segmen sebagai antar muka. Decoder tersebut terbentuk dari pintu-pintu akal yang masukannya berbetuk digit BCD dan keluarannya berupa saluran-saluran untuk mengemudikan tampilan 7 segmen.

Tabel Pengaktifan Seven Segment Display

7-Segment Display adalah komponen penampil angka (0–9) yang tersusun dari 7 buah LED (Light Emitting Diode) berbentuk huruf “8”. Setiap LED disebut segmen, diberi nama a, b, c, d, e, f, g, dan dapat dinyalakan secara kombinasi untuk menampilkan angka tertentu.

Pada 7-segment Common Cathode, setiap LED menyala jika:

- Katoda dihubungkan ke GND (0V)

- Anoda segmen diberi logika HIGH (+5V)

Misalnya, untuk menyalakan segmen “a”, cukup beri logika 1 ke pin “a”.

Counter digital (IC 4026, 74LS90 + 74LS47)

Display penghitung langkah atau waktu

Sistem kontrol penyiram tanaman otomatis (seperti milikmu)

Pada 7-segment Common Cathode, setiap LED menyala jika:

- Katoda dihubungkan ke GND (0V)

- Anoda segmen diberi logika HIGH (+5V)

Misalnya, untuk menyalakan segmen “a”, cukup beri logika 1 ke pin “a”.

Counter digital (IC 4026, 74LS90 + 74LS47)

Display penghitung langkah atau waktu

Sistem kontrol penyiram tanaman otomatis (seperti milikmu)

→ IC 4026 menghitung jumlah penyiraman dan menampilkannya pada 7-segment Common Cathode

4. Percobaan [Kembali]

a) Prosedur [Kembali]

b) Hardware [Kembali]

c) Rangkaian Simulasi dan Prinsip Kerja [Kembali]

Prinsip Kerja :

- Sensor Touch

Prinsip Kerja Sensor Touch (Pemberi Pakan)

Sensor touch digunakan sebagai input manual untuk memberi pakan ikan. Sensor ini bekerja berdasarkan perubahan kapasitansi saat disentuh oleh jari pengguna. Ketika sensor disentuh, terjadi perubahan sinyal logika pada keluaran sensor dari kondisi LOW menjadi HIGH. Sinyal keluaran ini kemudian diproses oleh rangkaian logika/digital (misalnya IC logika dan driver tampilan) untuk mengaktifkan aktuator pemberi pakan, seperti motor atau mekanisme mekanis tertentu. Dengan demikian, pemberian pakan dapat dilakukan secara sederhana dan cepat hanya dengan sentuhan, tanpa harus menyentuh pakan

- Sensor water level

Sensor water level berfungsi untuk mendeteksi ketinggian air di dalam akuarium. Sensor ini bekerja berdasarkan konduktivitas air, di mana semakin tinggi permukaan air yang menyentuh jalur sensor, semakin besar sinyal listrik yang dihasilkan. Sinyal dari sensor water level kemudian diolah oleh rangkaian penguat atau komparator (op-amp) untuk dibandingkan dengan tegangan referensi tertentu. Jika ketinggian air berada di bawah batas minimum (air rendah), keluaran rangkaian akan berubah ke kondisi aktif sehingga menghidupkan pompa air melalui transistor atau relay. Sebaliknya, ketika air telah mencapai batas maksimum (air tinggi), keluaran rangkaian akan berubah ke kondisi nonaktif sehingga pompa air dimatikan secara otomatis.

d) Flowchart [Kembali]

e) Video Demo [Kembali]

f) Download File [Kembali]

Download Datasheet Motor DC klik disini

Download Datasheet 7 Segment klik disini

Download Datasheet Gerbang OR klik disini

Download Datasheet Resistor klik disini